**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1990-03

### Recognition of VLSI module isomorphism

Zagourakis, Emmanouil N.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/30728

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

AD-A230 298

# NAVAL POSTGRADUATE SCHOOL Monterey, California

DTIC ELECTE JAN 0 3 1991

THESIS

RECOGNITION OF VLSI MODULE ISOMORPHISM

by

Emmanouil N. Zagourakis

March 1990

Thesis Advisor:

Chayn Yang

Approved for public release; distribution is unlimited

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                |                                                        | Form Approved<br>OMB No 0704-0188 |                   |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-----------------------------------|-------------------|---------------------------|

| 1a REPORT SECURITY CLASSIFICATION UNCLASS: IED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                | 16 RESTRICTIVE MARKINGS                                |                                   |                   |                           |

| 2a SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                | 3 DISTRIBUTION AVAILABILITY OF REPORT                  |                                   |                   |                           |

| 2b. DECLASSIFICATION / DOWNGRADING SCHEDU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LE                                             | Approved for public release; distribution is unlimited |                                   |                   |                           |

| 4. PERFORMING ORGANIZATION REPORT NUMBER(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                | 5 MONITORING ORGANIZATION REPORT NUMBER(S)             |                                   |                   |                           |

| 6a NAME OF PERFORMING ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7a NAME OF MONITORING ORGANIZATION             |                                                        |                                   |                   |                           |

| Naval Postgraduate School                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (If applicable)<br>EC                          | Naval Postgraduate School                              |                                   |                   |                           |

| 6c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                | 7b ADDRESS (City, State, and ZIP Code)                 |                                   |                   |                           |

| Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                | Monterey, CA 93943-5000                                |                                   |                   |                           |

| 8a. NAME OF FUNDING / SPONSORING ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9 PROCUREMENT INSTRUMENT COENTIFICATION NUMBER |                                                        |                                   |                   |                           |

| 8c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                | 10 SOURCE OF FUNDING NUMBERS                           |                                   |                   |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                | PROGRAM<br>ELEMENT NO                                  | PROJECT<br>NO                     | TASK<br>NO        | WORK UNIT<br>ACCESSION NO |

| 11 TITLE (Include Security Classification) RECOGNITION OF VLSI MODULE ISOMORPHISM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |                                                        |                                   |                   |                           |

| 12 PERSONAL AUTHOR(S) ZAGOURAKIS, Emmanouil N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |                                                        |                                   |                   |                           |

| 13a TYPE OF REPORT 13b TIME CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 DATE OF REPO<br>1990 Marc                   |                                                        |                                   | PAGE COUNT<br>151 |                           |

| 16 SUPPLEMENTARY NOTATION The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the US Government.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                                        |                                   |                   |                           |

| 17 COSATI CODES  18 SUBJECT TERMS (Continue on reverse if necessary and identify by block number)  FIELD GROUP SUB-GROUP VLSI circuit verification; gate recognition;  isomorphism identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |                                                        |                                   |                   |                           |

| The purpose of this study is to determine whether or not a program could be developed to examine isomorphism between parts of a VLSI layout. Many simulation files, obtained through Magic's hierarchical extractor, were analyzed in order to develop a C program to accomplish recognition in several types of gates. This recognition gives signatures in order to check for isomorphism.  The development and design of the algorithms used in different parts of the program are described. Results demonstrate that recognition of elements in a CMOS circuit is possible, even with moderate complexity structures. An appendix with the C program listings is included.  20 DISTRIBUTION: AVAILABILITY OF ABSTRACT STRUCTURES INCLUDED SAME AS RPT DICCUSERS UNCLASSIFIED.  21 ABSTRACT SECURITY (LASSIFICATION UNCLASSIFIED)  22 NAME OF RESPONSIBLE INDIVIDUAL 22 DIFFICE SYMBOL |                                                |                                                        |                                   |                   |                           |

| 22a NAME OF RESPONSIBLE INDIVIDUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22b TELEPHONE (                                | Include Area Code                                      |                                   |                   |                           |

| YANG, Chyan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 408-646-2                                      | 266                                                    | E                                 | C/Ya              |                           |

20 Fr.m 1473, JUN 86

#### Approved for public release; distribution is unlimited

Recognition of VLSI Module Isomorphism

by

Emmanouil N. Zagourakis Lieutenant, Hellenic Navy. B.S., Hellenic Naval Academy, 1980

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

#### NAVAL POSTGRADUATE SCHOOL

#### **ABSTRACT**

The purpose of this study was to determine whether or not a program can be developed to examine isomorphism between parts of a VLSI layout. Many simulation files, obtained through Magic's hierarchical extractor, were analyzed in order to develop a C program to accomplish recognition of several types of gates. This recognition gives signatures in order to check for isomorphism.

The development and design of the algorithms used in different parts of the program are described. Results demonstrate that recognition of elements in a CMOS circuit is possible, even with moderate complexity structures. An appendix with the C program listings is included.

| Accesi                                             | on For  | 1 |  |

|----------------------------------------------------|---------|---|--|

| NTIS CRA&I  DTIC TAB  U dia ourced  Justification: |         |   |  |

| By<br>Di t ib tio /                                |         |   |  |

| Availability Codes                                 |         |   |  |

| Di∵t                                               | Special | ĭ |  |

| A-1                                                |         |   |  |

### TABLE OF CONTENTS

| I.   | INT | RODUCTION                                 |

|------|-----|-------------------------------------------|

|      | A.  | BACKGROUND                                |

|      | B.  | SCOPE OF THE THESIS INVESTIGATION         |

|      | C.  | THESIS OUTLINE                            |

| II.  | GR  | APH THEORY - THE ISOMORPHISM PROPERTY     |

| III. | AN  | ALYSIS OF SIMULATION FILES                |

|      | A.  | FROM MAGIC TO SIMULATION FILES            |

|      | B.  | SIMULATION FILES                          |

| IV.  | AN  | ALYSIS AT TRANSISTOR LEVEL                |

|      | A.  | GROUPING OF TRANSISTORS                   |

|      | B.  | IMPLEMENTATION                            |

| V.   | EX  | AMINING .SIM FILES OF KNOWN CMOS CIRCUITS |

|      | A.  | RECOGNITION ALGORITHMS                    |

|      |     | 1. INVERTER                               |

|      |     | 2. PASSGATE                               |

|      |     | 3. 2-INPUT NOR                            |

|      |     | 4. 2-INPUT NAND                           |

|      |     | 5. 2-PHASE CLOCKED INVERTER               |

|      |     | 6. PRECHARGED INVERTER 18                 |

|      |     | 7. 2-INPUT PRECHARGED NOR                 |

|      |     | 8. 2-INPUT PRECHARGED NAND                |

|      | В.  | LENGTH AND WIDTH SIGNATURES               |

|      | C   | IMPLEMENTATION 50                         |

|       | D.   | PROGRAM ACCOMPLISHMENTS                           | 23  |

|-------|------|---------------------------------------------------|-----|

| VI.   | EX.  | AMINATION OF .SIM FILES FOR UNKNOWN CMOS CIRCUITS | 24  |

|       | A.   | STRUCTURES WITH PATH TO VDD AND GND               | 24  |

|       | В.   | STRUCTURES WITHOUT PATHS TO VDD AND GND           | 25  |

|       | C.   | IMPLEMENTATION                                    | 25  |

| VII.  | IDE  | ENTIFICATION FOR ISOMORPHISM                      | 28  |

|       | A.   | TRANSISTOR LEVEL                                  | 28  |

|       | B.   | GATE LEVEL                                        | 29  |

|       | C.   | STRUCTURE LEVEL                                   | 30  |

| VIII. | CO   | NCLUSIONS                                         | 31  |

|       | A.   | ISOMORPHISM                                       | 31  |

|       | B.   | FUTURE RESEARCH                                   | 31  |

| APPE  | ENDI | IX A: PROGRAM LISTINGS                            | 32  |

|       | A.   | GLOBAL VARIABLES                                  | 32  |

|       | B.   | GATE RECOGNITION PROCESS                          | 51  |

|       | C.   | STRUCTURE RECOGNITION                             | 89  |

|       | D.   | ISOMORPHISM VERIFICATION                          | 116 |

|       | E.   | OTHER FUNCTIONS                                   | 124 |

| REFE  | REN  | NCES                                              | 141 |

| INITI | AL I | DISTRIBUTION LIST                                 | 142 |

### LIST OF FIGURES

| 2.1 | Example of three graphs which are mutually isomorphic | 5  |

|-----|-------------------------------------------------------|----|

| 3.1 | A .sim file for an inverter.                          | 8  |

| 3.2 | A .sim file for an inverter, without labels.          | 10 |

#### ACKNOWLEDGMENT

I would like to express my appreciation to the faculty and staff of the Electrical and Computer Engineering department for providing me with the necessary tools for my future job. I would like to express special thanks to Professor Chyan Yang for his valuable assistance and for providing the necessary guidance and direction in accomplishing this research and formulating this document. I also wish to thank Professor Cotton for his valued assistance as my second reader. Finally, I am most grateful to my wife Poly for her understanding, patience, and support during my studies; and to my daughter Helen for just being mine.

#### I. INTRODUCTION

#### A. BACKGROUND

This thesis is an initial step to develop a tool for fast verification of Very Large Scale Integration (VLSI) circuit design and timing verification. The integration of VLSI chips includes many steps, beginning with setting the specifications and continuing to fabrication of the chips. Design verification checks the chip design before fabrication. The verification process is divided into three parts:

- Functional (logic) verification to ensure that the design gives the desired results.

- Physical (layout) verification to ensure that the physical layout obeys the geometric design rules and to validate the proper circuit connectivity.

- Timing verification to validate the path delays and check that they satisfy the duty cycle according to the design specifications.

The design process of a VLSI circuit leads toward the geometric layout. This geometric layout is used to generate the masks from which the chip is fabricated on wafers. The correctness of the geometric layout is crucial and must be checked before the mask generation process. Due to the complexity of the geometric layout mistakes can occur. Circuits that have been visually checked by designers and layout specialists have been found to have missing contacts when entering the mask shop. Errors like this are costly in terms of design time and, therefore, money. Computer aided design (CAD) tools can reduce the time needed for the design process. Development of a fast circuit verifier can reduce the design time.

A circuit verifier ensures that the design is accurate, reducing the chance of faulty chips. There are several studies which attempt to provide design verification in certain stages of the VLSI design process [1][2]. Some of them use the switch-level model and others the device-level model. Although the switch-level model gives faster results, component regularity can give the device level model the advantages of better identification for certain elements. By comparing structures which consist of certain elements, a quick verification can be achieved. For example, if the designer knows that his geometric layout contains 99,336 transistors, 8,952 inverters, 6,747 pacsgates, 125 XOR gates and so on, a CAD tool can test for these quantities and perform a quick verification. Beside the device counter process, a timing analysis based on gates (or in general, devices) can be faster by using devices than using transistors.

This research is concentrated on an algorithm that will provide designers with circuit verification. This algorithm accomplishes its task by examining the isomorphism property through the graph theory.

#### B. SCOPE OF THE THESIS INVESTIGATION

The goal of this thesis is to develop an algorithm that examines whether the isomorphism exists between a Complementary Metal Oxide Silicon (CMOS) circuit geometric layout and the expected layout. The expected design description may produce the expected simulation file before the layout process. By this algorithm, errors that have taken place during assembling the whole geometric layout from its distinct parts can be identified.

The algorithm uses a simulation file as input. This simulation file, consisting of transistors, is analyzed. We first perform gate recognition of several types of gates and remove the transistors which belong to these gates from the simulation file. The remaining transistors are grouped as abstract structures (devices). This gate and/or structure

recognition and taxonomy provides classification among transistors. Transistors of the same connection topology are grouped together. The above process is performed in the expected circuit and in the part of the circuit that we want to examine. The algorithm then performs tests for each kind of gate and structure to verify that the two circuits are isomorphic.

#### C. THESIS OUTLINE

Chapter II introduces graph theory and discusses briefly the isomorphism property.

In Chapter III, the different steps that are required to generate simulation files are examined (Magic-extractor-ext2sim).

The preliminary stage of structuring the transistor level information for later use is presented in Chapter IV.

Examination of simulation files for known CMOS circuits is presented in Chapter V. Several kinds of gates are recognized and their algorithms are analyzed.

Chapter VI provides the algorithm to group the rest of the existing transistors in structures with proper format, for later examination for isomorphism.

Chapter VII discusses the algorithm for the tests that are performed in order to identify if isomorphism exists.

Chapter VIII summarizes the results of this thesis and includes possible uses of this program in circuit and timing verification.

# II. GRAPH THEORY - THE ISOMORPHISM PROPERTY.

A graph, G, is a network of nodes or vertices (V) and arcs or edges (E) from some nodes to others or to themselves [3]. According to properties that exist between vertices and edges, graphs are categorized in a taxonomy that is quite lengthy. Some example categories are:

- 1. Simple, if no self-loops or multiple edges exist.

- 2. Directed, if the pair of end points of an edge is ordered.

- 3. Euler, every edge appears once if in an undirected graph.

- 4. Complete, if every pair of distinct vertices is adjacent.

- 5. Tree, if the graph has no cycles

and many others [3].

A graph can be used to represent a VLSI circuit layout, with transistors as the vertices of a graph and the connections between the transistors its edges. The only difference that exists is that the graph of a VLSI circuit, containing perhaps 100,000 transistors, cannot be placed in any of the above categories. The connectivity follows functional and topological requirements. These functional requirements establish the way of connectivity between the transistors and thus no assumption can be made in order to fit somewhere in graph theory's taxonomy.

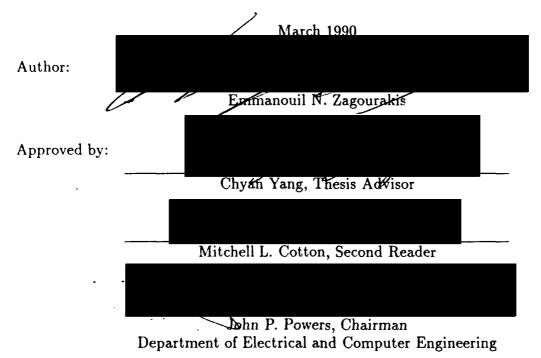

In graph theory two concepts of "sameness" exist. These concepts are equality and isomorphism. "Two graphs, G and G' are equal if they have equal vertex sets and

Figure 2.1: Example of three graphs which are mutually isomorphic.

equal edge sets" [4]. The isomorphic property is more fundamental one. "Isomorphic" has Hellenic roots meaning "same structure." Two graphs, G and G', are said to be isomorphic if a 1-to-1 mapping of graph G' onto graph G exists [5]. The verification of 1-to-1 mapping is not an easy task, especially if the number of vertices and edges is large. The three graphs in Figure 1 are isomorphic, although they don't seem to be at first glance. In fact, the graph isomorphism problem is NP-complete [6].

Isomorphism preserves a number of properties [4], some of which will be useful to this research. These are:

• Same number of vertices.

- Same number of edges.

- Same number of pieces (subgraphs).

If one of the above properties does not exist between two graphs, they are not isomorphic. In other words, either an attempt can be made to check for isomorphism or to try to prove that one of the above properties does not exist and the graphs are not isomorphic. The existence of isomorphism between two graphs, is based on "graph invariants." These are distinct properties or parameters that must exist in both graphs if they are isomorphic. The more graph invariants that can be identified, the more certainty exists about isomorphism. But this is a postulation, not a proof. A "complete graph invariant" is considered the one property that must exist between two isomorphic graphs, and is the only way to prove isomorphism. Since the discovery of such complete graph invariant, in a computable way, would solve the isomorphism problem, the search has been persistent and still continues [7][8].

In this research, the attempt to identify isomorphism is based on assigning graph invariants and examining for existence of the three properties mentioned before. This attempt is made through circuit layout gate recognition. The taxonomy of different structures of transistors into gates, implies all three properties. For example, suppose 1,932 inverters exist in a circuit. This means that by recognizing structures as inverters, in the two graphs, and comparing them we have already examined for the first two properties (same vertices and same edges). Furthermore, having the same number of inverters, the third property is also examined. Of course, as mentioned before, this is a postulation not a proof as the gates may be connected in the wrong way. The larger the number of structures which are identified, the less the uncertainty is. This thesis treats the isomorphism at the gate level but more levels can be applied to prove whether isomorphism exists or not.

#### III. ANALYSIS OF SIMULATION FILES.

The simulation file of a CMOS layout plays a very important role in this thesis. The simulation file is the input to the verification program which was implemented. Since it is used as the source for the needed information for the CMOS layout, it is necessary to discuss the way it is created and the information contained in its lines.

#### A. FROM MAGIC TO SIMULATION FILES

Computer-aided design (CAD) tools play an important role in the design of VLSI layouts. Several tools have been developed to assist VLSI designers. One such tool for CMOS technology layouts is Magic [9].

Magic was developed by the faculty and students at University of California, Berkeley (UCB) in 1983. It is an interactive system for creating VLSI circuit layouts. It consists of interactive packages, the most important functions of which are:

- Mead-Conway style of design. This implies simplified design rules and circuit structures.

- 2. Capability for designs of Manhattan-style layouts. This means that the edges in the layout are vertical or horizontal.

- 3. Capability for MOSIS-scalable CMOS design rules. Magic's name for this technology is SCMOS.

- 4. Hierarchical circuit extraction used to convert the graphical layout into a Caltech Intermediate Form (CIF) file.

In order to generate a simulation file, several steps must occur. A VLSI layout can be designed using Magic. The result of this design is a file with the extension .mag.

```

I units: 150 tech: scmos

p D Vdd Q 2 4 78 8

n D GND Q 2 4 78 -10

R GND 839

C Q GND 58

R Q 878

C D GND 13

R D 488

C Vdd GND 47

R Vdd 919

```

Figure 3.1: A .sim file for an inverter.

By using the extractor program which is in the Magic package, we come up with a CIF representation of the file. The extension of this file is now .ext. This .ext file contains informations such as transistor dimensions, circuit connectivity, and resistance and capacitance values between the different nodes of the circuit. The .ext file, which is the hierarchical representation of the original layout, is converted to its flat representation. This is the simulation file and it has extention .sim. This transformation is done by another UCB tool named ext2sim.

This discussion about Magic does not widely cover the subject, and the interested reader may find a lot of detailed information in [10].

#### **B. SIMULATION FILES**

It is of great importance to identify the information provided by the simulation file. Figure 3.1 illustrates the .sim file of an inverter.

The .sim file begins with a header line which contains the scale factor (150) and the technology (scmos) of the circuit. Some simulation files may have another field describing the format. In this thesis, scmos technology is required in the technology field (Berkeley or MIT).

Next, the transistor lines follow. Each transistor has its own line, including information about this transistor. Eight fields exist in the transistor line, which, in sequence, are:

- 1. Transistor type (p or n).

- 2. Gate field, which contains the node label for the gate.

- 3. Source field, which contains the node label for the source.

- 4. Drain field, which contains the node label for the drain.

- 5. Length field, which contains the scaled length of the transistor.

- 6. Width field, which contains the scaled width of the transistor.

- 7. X-location, field which indicates the location of a center point inside the transistor.

- 8. Y-location, field which indicates the location of a center point inside the transistor.

In this thesis, the first six fields are considered to provide us with useful information. The labels Vdd and GND which appear in a .sim file, indicate a connection with the common voltage source and ground of the circuit. This label is placed either in the source or in the drain field. This placement is performed by the extraction process. It is done in a manner depending on the position of the gates in the layout. For example, a gate can be rotated, inverted and so on. Accordingly, the Vdd or GND label can be interchanged between source and drain fields. That has nothing to do with the functionality of the transistors. A certain gate remains the same no matter where the Vdd and GND are placed.

```

| units: 150 tech: scmos

p 3_147_529 Vdd 3_955_744 2 4 78 8

n 3_147_529 GND 3_955_744 2 4 78 -10

R GND 839

C 3_955_744 GND 58

R 3_955_744 878

C 3_147_529 GND 13

R 3_147_529 488

C Vdd GND 47

R Vdd 919

```

Figure 3.2: A .sim file for an inverter, without labels.

extraction process assigns numerical labels to all of them. An example of such assignment is illustrated in Figure 3.2. Because of this, there are no unlabeled nodes within a layout. In our further research we will consider that labels exist in all fields in a transistor line.

#### IV. ANALYSIS AT TRANSISTOR LEVEL.

Initial research was conducted to specify the most efficient approach. This was needed not only to achieve the final goal of identification for isomorphism, but also decrease the execution time of the program.

#### A. GROUPING OF TRANSISTORS

As it was stated in Chapter 2, the more graph invariants (signatures) we identify in a circuit layout, the more certainty exists about the isomorphism property. Initially, the transistors are divided into two categories, P and N transistors. Furthermore, each of these categories can be divided into four categories:

- 1. P1: P transistors without connection to Vdd.

- 2. P2: P transistors with connection to Vdd.

- 3. N1: N transistors without connection to GND.

- 4. N2: N transistors with connection to GND.

Notice that there are no P transistors connected to GND nor N transistors connected to Vdd due to the complementary technology of CMOS.

#### **B. IMPLEMENTATION**

A C program (see Appendix A) was written to implement this prelimenary process.

The first step in this program is to accept a .sim file as input. The program start running by the command "iso" followed by one or two file names of .sim files. If one filename is invoked, the program performs just device counting. If two filenames are

invoked, it performs examination for isomorphism between them. These two files have to be in order. That means, the first file cannot be smaller than the second one. From now on we are going to refer to them as big (the first file) and small (the second file) even though they might be equivalent (having same number of transistors).

The program then, opens this file (or these files), and creates a file named "isooutput", which contains all information from the recognition process. The information

contains the labels for input, output, phase and whatever else is helpful for the program

or the designer. It will also contain all error messages that may be prompted during the

program's execution.

After the program accepts its inputs, it first checks that they are in proper format. This is done by examining the headers of the .sim files. In case the specifications are not met, an error message is prompted and the program is terminated.

Then the program creates dummy head and tail pointers for the four linked lists. These four lists are going to contain information for the transistors. Next, the rest of the input files are read. Each line is read and all information stored in a temporary structure. The process then continues the following 8 steps:

- 1. The first field is examined to see whether it is p or n.

- 2. If it is p, it is examined for existence of Vdd label in either source or drain fields.

- 3. If it has a Vdd label, this label is placed only in the source field. Then the remaining of information is placed in a structure which is pointed to by the P2 linked list.

- 4. If it does not have a Vdd label, the information on this transistor is placed in a structure which is pointed to by the P1 linked list.

- 5. If the first field is n, it is examined for GND label in either source or drain fields.

- 6. If it has a GND label, this label is placed only in the source field. Then the rest of the information is placed in a structure which is pointed by the N2 linked list.

- 7. If it does not have a GND label, the information on this transistor placed in a structure which is pointed to by the N1 linked list.

- 8. Read in the next line. If transistor information is in the line go to step 1; otherwise the program continues with the recognition process.

# V. EXAMINING .SIM FILES OF KNOWN CMOS CIRCUITS.

An important goal of this research was to determine whether or not known CMOS circuits can be recognized. Previously-conducted research [10] showed that this could be done and also can be extented to more types of circuits. This thesis recognizes the following 8 types of gates:

- 1. Inverter.

- 2. Passgate.

- 3. 2-input NOR.

- 4. 2-input NAND.

- 5. Precharged inverter.

- 6. 2-phase clocked inverter.

- 7. 2-input precharged NOR.

- 8. 2-input precharged NAND.

The major factor for the selection of the above gates, was the existence of these gates in the VLSI circuits library at NPS. Integrated tools can be used for the benefit of NPS students, if these tools can cooperate and function together.

The circuits of these gates were designed using MAGIC and, through the extraction process, were hierarchically presented. The extracted files were converted to UCB CIF format files, using the ext2sim procedure [9]. The ext2sim program created the

needed .sim files. These simulation files were analyzed to identify the algorithm for their recognition.

Several tests were conducted with .sim files. These files were either selected from the NPS student projects or created for the purpose of this research. Testing files were necessary because, for each type of gate, many arrangements of the labels in the different fields may exist. Because the extraction process places the source and drain field labels interchangeably we must carefully choose various testing files in order to exhaustively test all possible configurations of these gates.

We discuss further details of the recognition process of each gate type in the next two sections.

#### A. RECOGNITION ALGORITHMS

The recognition algorithms are described next. The algorithms use the four transistor lists which are named P1, P2, N1 and N2. In some gates, there are more than one transistor from the same linked list. This case is resolved by referring to N11, N12 for N1 list, for example. The algorithms are:

#### 1. INVERTER

- 1. Obtain a p-type and an n-type transistor, from the P2 and N2 linked lists, respectively.

- 2. If gates and drains of P2 and N2 are the same, an inverter is found; otherwise, continue with a different set of p and n transistors, taken from the P2 and N2 lists.

- 3. If no other set remains, exit the inverter recognition process.

#### 2. PASSGATE

1. Obtain a p-type and an n-type transistor, from the P1 and N1 linked lists, respectively.

#### 2. If:

- (a) Sources of P1 and N1 are the same, and different from all other fields.

- (b) Drains of P1 and N1 are the same, and different from all other fields.

- (c) Gates of P1 and N1 are different,

then, a passgate is found; Otherwise, continue with a different set of p and n transistors from P1 and N1 lists.

#### 3. 2-INPUT NOR

Obtain two p-type and two n-type transistors from P1, P2. N2 and N2 linked lists.

We will refer to each N2 as N21 and N22, respectively.

#### 2. If:

- (a) Gates of P2 and N21 are the same, and different from all other labels.

- (b) Gates of P1 and N22 are the same, and different from all other labels.

- (c) Drains of N21 and N22 are the same, and

- Drain of P22 is the same as the source of P1.

- Drain of N21 (or N22) is the same as the drain of P1,

or,

- Drain of P2 is the same as the drain of P1.

- Drain of N21 (or N22) is the same as the source of P1,

then, a 2-input NOR gate is found; Otherwise, continue with different set of transistors, taken from P1, P2, N2 and N2 lists.

3. If no other set remains, exit the 2-input NOR gate recognition process.

#### 4. 2-INPUT NAND

- Obtain two p-type and two n-type transistors from P2, P2, N1 and N2 linked lists.

We will refer to each P2 as P21 and P22, respectively.

- 2. If:

- (a) Gates of P21 and N2 are the same, and different from all other labels.

- (b) Gates of P22 and N1 are the same, and different from all other labels.

- (c) Drain of P21 and P22 are the same, and

- Drain of P21 (or P22) is the same as the source of N1.

- Drain of N2 is the same as the drain of N1.

or,

- Drain of P21 (or P22) is the same the drain of N1.

- Drain of N2 is the same as the source of N1,

then, a 2-input NAND gate is found; Otherwise, continue with different set of transistors, taken from P2, P2, N1 and N2 lists.

3. If no other set remains, exit the 2-input NAND gate recognition process.

#### 5. 2-PHASE CLOCKED INVERTER

- Obtain two p-type and two n-type transistors from P1, P2, N1 and N2 linked lists, respectively.

- 2. If:

- (a) Gates of P2 and N2 are the same, and different from all other labels.

- (b) Gates of P1 and N1 are different from each other and from all other labels, and

- Drain of P2 is the same as the source of P1.

- Drain of N2 is the same as the source of N1.

- Drain of P1 is the same as the drain of N1,

- Drain of P2 is the same as the source of P1.

- Drain of N2 is the same as the drain of N1.

- Drain of P1 is the same as the source of N1,

or,

- Drain of P2 is the same as the drain of P1.

- Drain of N2 is the same as the source of N1.

- Source of P1 is the same as the drain of N1,

or.

- Drain of P2 is the same as the drain of P1.

- Drain of N2 is the same as the drain of N1.

- Source of P1 is the same as the source of N1.

then, a 2-phase clocked inverter is found; Otherwise, continue with different set of transistors, taken from P1, P2, N1 and N2 lists.

3. If no other set remains, exit the 2-phase clocked inverter recognition process.

#### 6. PRECHARGED INVERTER

- 1. Obtain a p-type and two n-type transistors from P2, N1 and N2 linked lists, respectively.

- 2. If:

- (a) Gates of P2 and N2 are the same.

- (b) Gates of P2 and N2 are different from all other labels, and

- Drain of P2 is the same as the source of N1.

- Drain of N2 is the same as the drain of N1,

- Drain of P2 is the same as the drain of N1.

- Drain of N2 is the same as the source of N1,

then, a precharged inverter is found; Otherwise, continue with different set of transistors, taken from P2, N1 and N2 lists.

3. If no other set remains, exit the precharged inverter recognition process.

#### 7. 2-INPUT PRECHARGED NOR

- 1. Obtain one p-type and three n-type transistors from P2, N1, N1 and N2 linked lists. We will refer to each N1 as N11 and N12, respectively.

- 2. If,

- (a) Gates of P2 and N2 are the same, and different from all other labels.

- (b) Gates of N11 and N12 are different from each other, and from all other labels, and

- Drain of P2 is the same as the drain of N11 and the drain of N12.

- Drain of N2 is the same as the source of N12 and the source of N11.

or,

- Drain of P2 is the same as the source of N11 and the drain of N12.

- Drain of N2 is the same as the source of N12 and the drain of N11.

- Drain of P2 is the same as the source of N11 and the source of N12.

- Drain of N2 is the same as the drain of N11 and the drain of N12,

- Drain of P2 is the same as the drain of N11 and the source of N12.

- Drain of N2 is the same as the drain of N12 and the source of N11,

then, a 2-input precharged NOR gate is found; Otherwise, continue with different set of transistors, taken from P2, N11, N12 and N2 lists.

3. If no other set remains, exit the 2-input precharged NOR recognition process.

#### 8. 2-INPUT PRECHARGED NAND

- 1. Obtain one p-type and three n-type transistors from P2, N1, N1 and N2 linked lists. We will refer to each N1 as N11 and N12, respectively.

- 2. If,

- (a) Gates of P2 and N2 are the same and different from all other labels.

- (b) Gates of N11 and N12 are different from each other and from all other labels, and

- Drain of P2 is the same as the source of N11.

- Drain of N2 is the same as the source of N12.

- Drain of N11 is the same as the drain of N12, and different from all other labels,

or,

• Drain of P2 is the same as the source of N11.

- Drain of N2 is the same as the drain of N12.

- Drain of N11 is the same as the source of N12, and different from all other labels,

- Drain of P2 is the same as the drain of N11.

- Drain of N2 is the same as the source of N12.

- Source of N11 is the same as the drain of N12, and different from all other labels,

or,

- Drain of P2 is the same as the drain of N11.

- Drain of N2 is the same as the drain of N12.

- Source of N11 is the same as the source of N12, and different from all other labels,

then, a 2-input precharged NAND gate is found; Otherwise, continue with different set of transuistors, taken from P2, N11, N12 and N2 lists.

3. If no other set remains, exit the 2-input precharged NAND gate recognition process.

#### B. LENGTH AND WIDTH SIGNATURES

Through the recognition process of each gate, another process is also performed. This process consists of placing the individual transistor information about length and width in the appropriate field of gate's structure. For example, if the two transistors which constitute an inverter have:

- 1. Length of p equal to 2.

- 2. Length of n equal to 3.

- 3. Width of p equal to 4.

- 4. Width of n equal to 5,

then, a way must be found to include this sizing information in the sizing fields of the identified inverter. This is necessary because, when the isomorphism identification procedure starts, there must be a way to distinguish between inverters of different size.

The formation of the length and width gate labels follows certain rules. These rules are referring to the lengths of p-type transistors; however, the same scheme is applied to n-type transistors or widths. These rules are:

- The length field for each gate is divided into two parts. The first part refers to p-type transistor lengths and the second to n-type transistors. The separation between the values of p-type and n-type transistors is marked by "-".

- If a circuit consists of more than one p-type transistor, two possibilities exist. Either, all the lengths are the same or they are not. If all lengths are the same, then only one length value appears; otherwise, all lengths appear, separated by "2".

#### C. IMPLEMENTATION

A program (see Appendix A) was written in C to implement the gate recognition process. The implementation includes additional steps. These are:

- 1. Creation of dedicated linked lists, one for every type of gate. These lists point to structures that include the necessary information for each type of gate.

- 2. Execution of the recognition process for each type of gate.

- 3. If no gate is found (for a particular type of gate), continue with recognition of another type of gate.

- 4. Whenever a gate is found, then:

- Perform the length and width placement process, according to the rules described in the previous section of this Chapter.

- Perform recognition of the labels for "input", "output", "phase", and others.

This information is needed as the output file will not include information on all transistors. It will include only information about the gate as a circuit.

- Place the necessary information of each gate in a structure. This structure is pointed to by the appropriate linked list.

- Remove the transistors that constitute the recognized gate.

- 5. Print all gates, with all appropriate information, in the output file.

#### D. PROGRAM ACCOMPLISHMENTS

The writing and testing of the previously described recognition process completes an important phase of this thesis. The recognition of these gates demonstrates the possibility and capability to identify more gate structures within a CMOS layout. However, we have to admit that exhaustive recognition is inefficient in computation time. For example, it may not be needed to search for numerous gates, if there is a small layout in which very few gate types exist.

# VI. EXAMINATION OF .SIM FILES FOR UNKNOWN CMOS CIRCUITS.

In Chapter V, it was examined how certain gates can be recognized. The next step is to group the remaining transistors in a useful way. This final task is the examination for existence of isomorphism property. As was stated in Chapter V, whenever a certain gate is recognized, the transistors that constitute this gate are removed from the appropriate linked list.

The remaining transistors in the layout can be divided in two categories [10]. These are:

- Groups of transistors that constitute structures with connection to Vdd and GND, with an existing path between them.

- Groups of transistors that constitute structures without paths to Vdd or GND.

#### A. STRUCTURES WITH PATH TO VDD AND GND

The algorithm for identification of structures with a path to Vdd and GND requires the following steps:

- 1. A transistor is selected, with the Vdd label in its source field.

- 2. A search begins to find all transistors which are connected to the selected transistor's source or drain.

- 3. A recursive process takes place in order to identify all connected transistors.

- 4. When a connection to GND is found in any of the connected transistors, the process is considered complete. If no connection to GND is found, there is a possible error.

5. The above process is continued until no remaining transistor exist with connectivity to Vdd and GND within the .sim file.

#### B. STRUCTURES WITHOUT PATHS TO VDD AND GND

In order to continue with this step, the previous process must be complete. The algorithm for identification of these structures requires the following steps:

- 1. Select a remaining transistor in the .sim file.

- 2. Find all transistors which are connected to the selected one.

- 3. Recursively find all connected transistors.

- 4. If no other transistor exist in the .sim file, the process is considered complete.

Notice that there are cases in which all steps of the above process are not needed. For example, if we have a single transistor which is not included in a bigger structure, we need only the first two steps.

#### C. IMPLEMENTATION

The actual implementation of the previously mentioned algorithms includes more steps. This is necessary as managerial procedures have to be added. These procedures play an important role in the correct and efficient execution of the program.

The program first allocates space for a two-dimensional array. This array includes the information needed from these structures. The first field in the array contains the device number. The second field contains pointers to all transistors that constitute the structure. Because these structures (devices) do not have a standard form, we cannot use the same data structure format as before. Redimensioning of the structures and its elements is also necessary to give flexibility. This is important, especially if memory space is limited and a large circuit is examined. However, redimensioning was considered

easier and faster than changing the data structure and parts of the program each time a new circuit is analyzed.

The next step merges the four linked lists into two. The P1 and P2 lists are combined in one, as well as the N1 and N2 lists. This is necessary as abstract devices can have any formation of transistors. The formation must always follow the CMOS general structure, which is, group of P transistors connected to Vdd, followed by N transistors connected to GND.

Then, a search takes place to find a transistor whose gate, source or drain includes the label Vdd. If one (or the first) is found, it is removed from the linked list. This will reduce the execution time, as this transistor will not be selected again.

The search continues along the p-type and n-type transistor lists, to identify transistors that are connected to the chosen one. A recursive search continues until all connected transistors, in the p-type and n-type lists, are reached.

A checking procedure follows, to determine whether or not a connection to GND exist. If no such connection exists, there is a possible error. However, a designer may have transistors within a circuit, which are constantly high or low. This can happen for functional purposes of the circuit. In that case, an error message acts interactively by asking the user whether he wishes to reexamine the .sim file, because no path to GND exists. If the user answers yes, the program is terminated. If the user answers no, the program places this structure as a device and continues its execution.

All transistors that were identified as a structure are placed into an array. The device counter is incremented and the search process starts again. It continues until no other structure with a path from Vdd to GND exists.

The two linked lists with the remaining transistors are combined into a single list. The first transistor of this list is selected and placed on the top of a stack. This transistor is removed from the linked list.

Then recursively compare all transistors which are connected to the selected one. All these transistors are placed on the stack and removed from the linked list. When no other transistor is found which is connected to this device, each transistor of the stack is placed into device array. The algorithm repeats the same process for the current "first" transistor. If no other transistor is left in the single linked list, this phase is considered complete.

# VII. IDENTIFICATION FOR ISOMORPHISM.

The isomorphism identification is structured based on the levels discussed in previous Chapters. It is performed at transistor level, gate level and structure level. In each of them, different signatures (properties) are examined and different graph invariants are considered. These differences occur from the variance in information that can be extracted. We now analyze the different factors that are important in isomorphism checking for each level..

### A. TRANSISTOR LEVEL

As mentioned in Chapter IV, the transistors that exist in every .sim file are placed in four separate linked lists. This placement was done according to whether or not a connection from Vdd to GND exits. This taxonomy of transistors gives the qualitative property that we are going to use. The number of transistors in each linked list is the needed graph invariant. Four quantative comparisons are performed between transistors of the two files:

- 1. Numerical comparison between the P1 list of the one file and the P1 list of the other file.

- 2. Numerical comparison between the P2 list of the one file and the P2 list of the other file.

- 3. Numerical comparison between the N1 list of the one file and the N1 list of the other file.

- 4. Numerical comparison between the N2 list of the one file and the N2 list of the other file.

If the big file has fewer transistors of any type than the small file does, no isomorphism exists between them. If the big file has the same or more, we simply have an indication that isomorphism may exist between them.

#### B. GATE LEVEL

After the gate recognition process is done to both files, two linked lists exist for each type of gate. Each list contains gates of a given type, one from the big file and another from the small file. The needed signatures come from the taxonomy which has already been performed. The identification, for example, of an inverter implies two transistors (a p-type and a n-type), connected in a certain way as it can be seen in Figure 3.1; the gates connected together, as well as the drains connected together. Source-field of p-type connected to Vdd and source-field of n-type connected to GND.

Furthermore, beside the connectivity implied by this taxonomy, more signatures are tested. The length and the width of each gate were considered to be sufficient signatures. The length and width preserved, as mentioned in Chapter V, the lengths and widths of all transistors that constitute a particular gate. Three comparisons are performed between the lists of a given type gates of the two .sim files:

- Numerical. If, for example, the big file has fewer inverters than the small one, no isomorphism exists.

- Qualitative in lengths. A type of gate may be numerically in order, between the two files, but the gates may differ. They do not differ in type, but in lengths. This is the reason for such a comparison.

- Qualitative in widths. Same comparisons are performed, and for the same reasons, as stated before.

# C. STRUCTURE LEVEL

The structure identification process results in the creation of two linked lists, one list for the structures of each file. Isomorphism is verified by examining if a structure which exists in the second file exists also in the first. During this procedure, structures with same total number of transistors are compared. Four types of comparisons are performed:

- 1. Numerical comparisons between p-type transistors that are connected to Vdd.

- 2. Numerical comparisons between p-type transistors that are not connected to Vdd.

- 3. Numerical comparisons between n-type transistors that are connected to GND.

- 4. Numerical comparisons between n-type transistors that are not connected to GND.

A structure that consists of a set of certain types of transistors must exist in both files in order for isomorphism to be valid.

# VIII. CONCLUSIONS.

#### A. ISOMORPHISM

The program, which is provided within Appendix A, achieves the primary goal of this thesis. This goal was to determine whether examination for isomorphism between two files could be performed. This goal was met through the gate recognition process. Algorithms for each separate type of gate were provided and implemented. This gate recognition process gives the capability for the program to run in two ways, to check for isomorphism or perform device counting. The algorithm's implementation and successful testing verifies the accomplishment of the primary goal.

#### B. FUTURE RESEARCH

Due to the complexity of VLSI circuits, tools to verify the correctness of a design are considered extremely important. Their importance comes from the additional design time and cost needed to correct design errors. This research gives another tool to the designer to verify the correctness of the design. This research is considered as a part of the initial stage of a much larger VLSI design and timing verifier.

# APPENDIX A: PROGRAM LISTINGS

## A. GLOBAL VARIABLES

```

* EMMANOUIL N. ZAGOURAKIS THESIS

MAR 1990

* This part of the program contains the common definitions.

#include <string.h>

#include <stdio.h>

#include <malloc.h>

* Macro definitions.

#define Function

#define TRUE 1

#define FALSE (!TRUE)

#define IsWhite(x) ((x=='\n') || (x==' ') || (x=='\t'))

#define IsDigit(x) ((060 <= x) && (x <= 071))

#define MAXLEN 50

#define MALLOC(x) ((x *) malloc(sizeof(x)))

#define NUMDEVICE 100

#define NUMTRANS 100

#define ERRTBL 43

/***********************************

* Transistor contains a pointer to the trans type; it also contains pointers *

* to gate, source, drain, length and width of the transistor; it also contains*

* a pointer to the next transistor in the linked list.

typedef struct transistor

char *type;

char *gate;

char *source;

char *drain;

char *length;

char *width;

```

```

struct transistor *next;

} trans;

trans *newp1;

trans *newp2;

trans *newn1;

trans *newn2;

trans *curr;

trans *curr1;

trans *(structure[NUMDEVICE][NUMTRANS]);

trans *(structure1[NUMDEVICE][NUMTRANS]);

trans *(stack[NUMTRANS]);

trans *(stack1[NUMTRANS]);

* Definitions of the pointers in different gate structures.

****************************

typedef struct inverter

int flag;

char *input;

char *output;

char *length;

char *width;

struct inverter *next;

} inv;

typedef struct prechargedinverter

int flag;

char *input;

char *output;

char *phase;

char *length;

char *width;

struct prechargedinverter *next;

}preinv;

typedef struct i2phclinverter

int flag;

char *input;

char *output;

```

```

char *php;

char *phn;

char *length;

char *width;

struct i2phclinverter *next;

}i2clinv;

typedef struct passgate

int flag;

char *terminal1;

char *terminal2;

char *php;

char *phn;

char *length;

char *width;

struct passgate *next;

}pass;

typedef struct nor2gate

int flag;

char *input1;

char *input2;

char *output;

char *length;

char *width;

struct nor2gate *next;

}nor2;

typedef struct nand2gate

int flag;

char *input1;

char *input2;

char *output;

char *length;

char *width;

struct nand2gate *next;

}nand2;

```

```

typedef struct prenand2gate

int flag;

char *input1;

char *input2;

char *phase;

char *output;

char *length;

char *width;

struct prenand2gate *next;

}prenand2;

typedef struct prenor2gate

int flag;

char *input1;

char *input2;

char *phase;

char *output;

char *length;

char *width;

struct prenor2gate *next;

}prenor2;

typedef struct temporary

char type[MAXLEN+1];

char gate[MAXLEN+1];

char source[MAXLEN+1];

char drain[MAXLEN+1];

char length[MAXLEN+1];

char width[MAXLEN+1];

} tem;

tem *temp;

* Definitions for head and tail pointers of the different linked lists.

************************************

typedef struct header

int length;

struct transistor *head, *tail;

```

```

} head_type;

head_type *header_new;

head_type *header1_new;

head_type *header_newp;

head_type *header_newn;

head_type *header1_newp;

head_type *header1_newn;

head_type *header_newp1;

head_type *header_newp2;

head_type *header_newn1;

head_type *header_newn2;

head_type *header1_newp1;

head_type *header1_newp2;

head_type *header1_newn1;

head_type *header1_newn2;

typedef struct headinv

int length;

struct inverter *head, *tail;

}inve:

inve *head_inv;

inve *head1_inv;

typedef struct headpreinv

int length;

struct prechargedinverter *head, *tail;

}preinve;

preinve *head_preinv;

preinve *head1_preinv;

typedef struct head2clinv

int length;

struct i2phclinverter *head, *tail;

}i2clinve;

i2clinve *head_2clinv;

i2clinve *head1_2clinv;

typedef struct headpass

```

```

int length;

struct passgate *head, *tail;

}passg;

passg *head_pass;

passg *head1_pass;

typedef struct headnor2

int length;

struct nor2gate *head, *tail;

}nor2g;

nor2g *head_nor2;

nor2g *head1_nor2;

typedef struct headnand2

int length;

struct nand2gate *head, *tail;

}nand2g;

nand2g *head_nand2;

nand2g *head1_nand2;

typedef struct headprenand2

int length;

struct prenand2gate *head,*tail;

}prenand2g;

prenand2g *head_prenand2;

prenand2g *head1_prenand2;

typedef struct headprenor2

int length;

struct prenor2gate *head, *tail;

}prenor2g;

prenor2g *head_prenor2;

prenor2g *head1_prenor2;

/***********************************

* Global variables.

***********************

```

```

/* pointer to the input big .sim file

*/

FILE *fp;

/* pointer to the input small file */

FILE *cp;

/* pointer to the detailed output file */

FILE *fo;

FILE *fopen();

FILE *fclose();

char buffer[MAXLEN+1];

char blank[MAXLEN+1];

* Integer declarations.

***********************************

int p1,p2,n1,n2;

int rec;

int totallength;

int totalwidth;

int pcount[NUMDEVICE];

int p1count[NUMDEVICE];

int p2count[NUMDEVICE];

int ncount[NUMDEVICE];

int n1count[NUMDEVICE];

int n2count[NUMDEVICE];

int tcount[NUMDEVICE];

int pcount1[NUMDEVICE];

int p1count1[NUMDEVICE];

int p2count1[NUMDEVICE];

int ncount1[NUMDEVICE];

int n1count1[NUMDEVICE];

int n2count1[NUMDEVICE];

int tcount1[NUMDEVICE];

int numdevice, numdevice1;

int stacknum, stacknum1;

int numtrans, numtrans1;

int ground;

int numn, nump;

int nump1, numn1;

* External functions.

extern head_type *create();

extern inve *createinv();

```

```

extern trans *newnode();

extern inv *NewInvert();

extern preinv *NewPreinv();

extern preinve *createpreinv();

extern pass *NewPass();

extern passg *createpass();

extern i2clinv *New2clinv();

extern i2clinve *create2clinv();

extern nor2 *Newnor2();

extern nor2g *createnor2();

extern nand2 *Newnand2();

extern nand2g *createnand2();

extern prenand2 *Newprenand2();

extern prenand2g *createprenand2();

extern prenor2 *Newprenor2();

extern prenor2g *createprenor2();

/***********************************

* Error messages issued by the program.

***********

***************

static char *msgtbl[ERRTBL] = {

"Reference file format error in field 1".

"Reference file format error in field 2, unit:",

"The system run out of storage space. ",

"Reference file format error in field tech:",

"Reference file format error in filed scmos ",

"Enter first the big .sim file and then the small .sim file.",

"No isomorphism! The big file has less p trans. w/o Vdd than the small file.",

"No isomorphism! The big file has less p trans. with Vdd than the small file.",

"No isomorphism! The big file has less n trans. w/o GND than the small file.",

"No isomorphism! The big file has less n trans. with GND than the small file.",

"No isomorphism! The big file has less inverters than the small file.",

"No isomorphism! An small file's inverter doesn't match with any of the big. ",

"No isomorphism! The small file has inverters but the big hasn't.",

"******The files are isomorphic in inverter structures.*********".

"No isomorphism! The big file has less 2ph.clock inverters than the small one.",

"No isomorphism! A small file's 2ph.clock inverter doesn't match with the big.",

"No isomorphism! The small file has 2ph. clock inverters but the big hasn't.",

"******The files are isomorphic in 2ph. clock inverter structures.****",

"No isomorphism! The big file has less NOR2 gates than the small file.",

"No isomorphism! A small file's NOR2 gates doesn't match with any of the big.",

"No isomorphism! The small file has NOR2 gates but the big hasn't.",

"*******The files are isomorphic in NOR2 gate structures.*******",

"No isomorphism! The big file has less NAND2 gates than the small file.",

```

```

"No isomorphism! A small file's NAND2 gates doesn't match with any of the big.",

"No isomorphism! The small file has NAND2 gates but the big hasn't.",

"********The files are isomorphic in NAND2 gate structures.*******",

"No isomorphism! The big file has less PRECH. NAND2 gates than the small one.",

"No isomorphism! A small file's PRECH. NAND2 gates doesn't match with the big.",

"No isomorphism! The small file has PRECH. NAND2 gates but the big hasn't.",

"******The files are isomorphic in PRECH. NAND2 gate structures.*****",